# **ATP Industrial Grade CompactFlash Card Specification**

Revision 3.6

### **Disclaimer:**

ATP Electronics Inc. shall not be liable for any errors or omissions that may appear in this document, and disclaims responsibility for any consequences resulting from the use of the information set forth herein.

The information in this manual is subject to change without notice.

ATP general policy does not recommend the use of its products in life support applications where in a failure or malfunction of the product may directly threaten life or injury.

All parts of the ATP documentation are protected by copyright law and all rights are reserved. This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior consent, in writing, from ATP Corporation.

The information set forth in this document is considered to be "Proprietary" and "Confidential" property owned by ATP.

### **Revision History**

| Date           | Version | Changes compared to previous issue                                       |  |  |

|----------------|---------|--------------------------------------------------------------------------|--|--|

| Aug.25th,2010  | 2.3     | - Update 16GB capacity                                                   |  |  |

|                |         | - Update certification and compliance                                    |  |  |

|                |         | - Update CHS Parameters                                                  |  |  |

|                |         | - Update Type II CF card information                                     |  |  |

| Jan.26th,2011  | 3.0     | - Support S.M.A.R.T. command                                             |  |  |

|                |         | - StaticDataRefresh and EarlyRetirement Technology                       |  |  |

|                |         | - Update performance                                                     |  |  |

|                |         | - Update MTBF                                                            |  |  |

|                |         | - Revise density                                                         |  |  |

| Feb.25th,2011  | 3.1     | - Revise Figure 4-1: ATP S.M.A.R.T. tool operation                       |  |  |

|                |         | - Revise UDMA mode 0~4                                                   |  |  |

| Apr.14th,2011  | 3.2     | - Add power failure protection feature                                   |  |  |

| Sep.30th,2011  | 3.3     | - Preliminary spec sheet of Industrial grade CF card with PowerProtector |  |  |

|                |         | feature                                                                  |  |  |

|                |         | - Update new P/N and performance                                         |  |  |

|                |         | - Update ATP branch/office contact information                           |  |  |

| Dec.16th, 2011 | 3.31    | - Official released version                                              |  |  |

|                |         | - Revise Table 3-19: Ultra DMA Data Burst Timing Requirements            |  |  |

|                |         | - Revise environment specifications                                      |  |  |

| Jan.31st, 2012 | 3.4     | - Add density 512MB/1GB/2GB                                              |  |  |

| Mar.14th, 2012 | 3.5     | - Add TBW (Total Bytes Written) information                              |  |  |

|                |         | - Revise StaticDataRefresh technology                                    |  |  |

| Nov. 8th, 2012 | 3.6     | - Revise table 2-1 system power table                                    |  |  |

# **Table of Contents**

| 1 | ATP    | INDUSTRIAL GRADE COMPACTFLASH CARD OVERVIEW                             | 5  |

|---|--------|-------------------------------------------------------------------------|----|

|   | 1.1    | ATP PRODUCT AVAILABILITY                                                | 4  |

|   | 1.2    | Introduction                                                            |    |

|   | 1.3    | Main Features                                                           |    |

|   | 1.4    | APPLICATION                                                             |    |

| 2 | PRO    | DUCT SPECIFICATION                                                      |    |

|   | 2.1    | SYSTEM POWER REQUIREMENT                                                |    |

|   | 2.1    | ENVIRONMENT SPECIFICATIONS                                              |    |

|   | 2.2    | RELIABILITY                                                             |    |

|   | 2.3    | PERFORMANCE PERFORMANCE                                                 |    |

|   | 2.4    | CHS Parameters                                                          |    |

|   | 2.6    | EXTRA FEATURES                                                          |    |

|   | 2.7    | GLOBAL WEAR LEVELING- LONGER LIFE EXPECTANCY                            |    |

|   | 2.8    | STATICDATAREFRESH TECHNOLOGY – ASSURE DATA INTEGRITY                    |    |

|   | 2.9    | ATP POWERPROTECTOR – BUILT-IN POWER DOWN DATA PROTECTION                |    |

|   | 2.10   | PHYSICAL DIMENSION SPECIFICATION                                        |    |

|   | 2.10   | MECHANICAL FORM FACTOR (UNITS IN MM)                                    |    |

|   | 2.11   | CERTIFICATION AND COMPLIANCE                                            |    |

|   | 2.12.  |                                                                         |    |

|   |        | ·                                                                       |    |

| 3 | ELE    | CTRICAL INTERFACE                                                       | 14 |

|   | 3.1    | PIN ASSIGNMENTS AND PIN TYPE                                            | 14 |

|   | 3.2    | ELECTRICAL DESCRIPTION                                                  |    |

|   | 3.3    | ELECTRICAL SPECIFICATION                                                | 24 |

|   | 3.3.1  | Input Leakage Current                                                   |    |

|   | 3.3.2  | Input Characteristics                                                   |    |

|   | 3.3.3  | Output Drive Type                                                       |    |

|   | 3.3.4  | Output Drive Characteristics                                            |    |

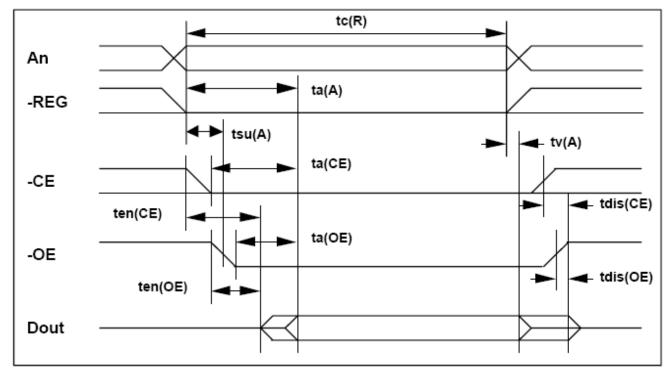

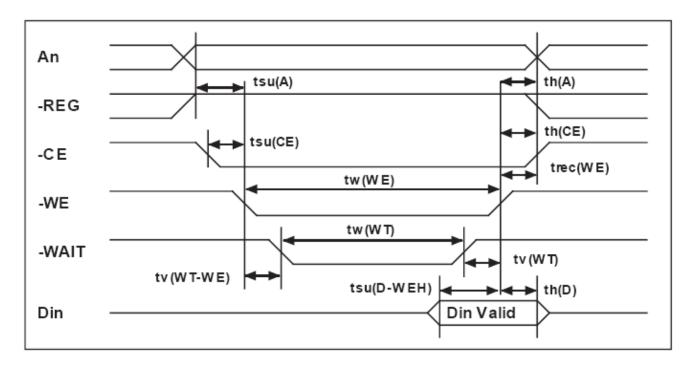

|   | 3.3.5  | Attribute Memory Read Timing                                            |    |

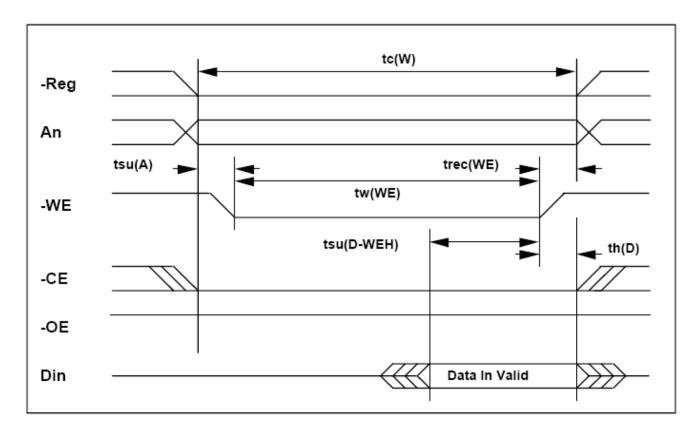

|   | 3.3.6  | Configuration Register (Attribute Memory) Write Timing Specification    |    |

|   | 3.3.7  | Common Memory Read Timing Specification                                 |    |

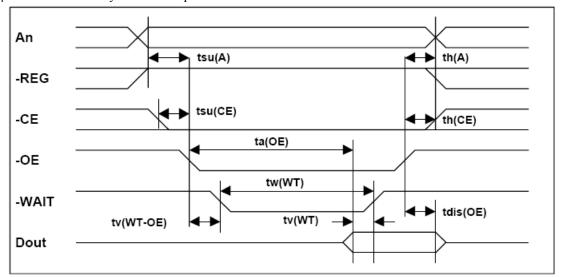

|   | 3.3.8  | Common Memory Write Timing Specification                                |    |

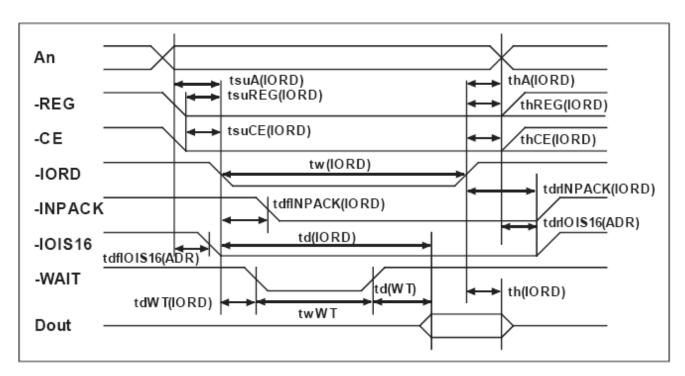

|   | 3.3.9  | I/O Input (Read) Timing Specification                                   |    |

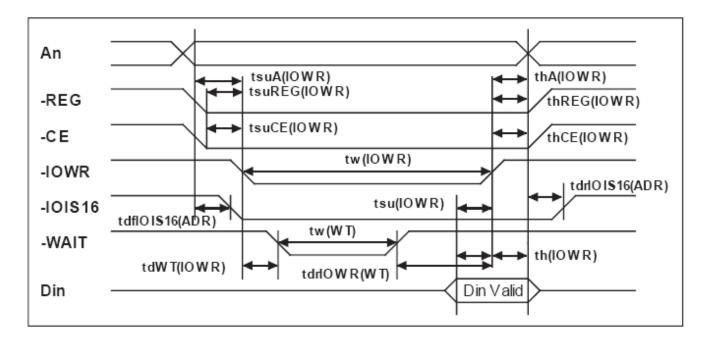

|   | 3.3.10 |                                                                         |    |

|   | 3.3.1  |                                                                         |    |

|   | 3.3.12 |                                                                         |    |

|   | 3.3.1. |                                                                         |    |

|   | 3.4    | CARD CONFIGURATION                                                      |    |

|   | 3.4.1  | CompactFlash Storage Card Registers and Memory Space Decoding           |    |

|   | 3.4.2  | Attribute Memory Function                                               |    |

|   | 3.4.3  | Configuration Option Register (Base + 00h in Attribute Memory)          |    |

|   | 3.4.4  | Card Configuration and Status Register (Base + 02h in Attribute Memory) |    |

|   | 3.4.5  | Pin Replacement Register (Base + 04h in Attribute Memory)               |    |

|   | 3.4.6  | Socket and Copy Register (Base + 06h in Attribute Memory)               |    |

|   | 3.5    | I/O Transfer Function                                                   |    |

|   | 3.6    | COMMON MEMORY TRANSFER FUNCTION                                         |    |

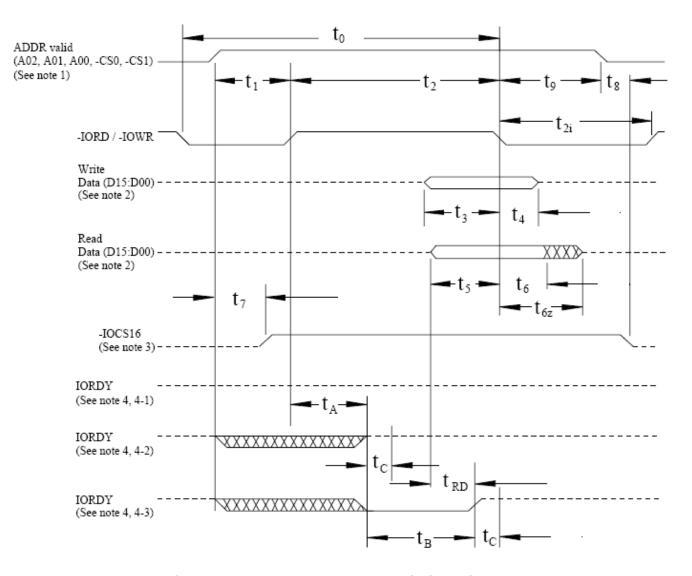

|   | 3.7    | TRUE IDE MODE I/O TRANSFER FUNCTION                                     |    |

|   | 3.8    | HOST CONFIGURATION REQUIREMENTS FOR MASTER/SLAVE OR NEW TIMING MODES    |    |

|   | 3.9    | TERMINATION RESISTORS FOR ULTRA DMA OPERATION                           | 64 |

| 4 | S.M. | A.R.T. FUNCTION                    | 65 |

|---|------|------------------------------------|----|

|   | 4.1  | S.M.A.R.T. FEATURE                 | 66 |

|   |      | S.M.A.R.T. FEATURE REGISTER VALUES |    |

|   | 4.3  | S.M.A.R.T. DATA STRUCTURE          | 66 |

|   | 4.4  | ATP S.M.A.R.T. TOOL                | 67 |

# 1 ATP Industrial Grade CompactFlash Card Overview

# 1.1 ATP Product Availability

Figure 1-1: ATP Product Availability

**Table 1-1: Capacities**

| ATP P/N        | CAPACITY |

|----------------|----------|

| AF512CFI-7ACXP | 512MB    |

| AF1GCFI-7ACXP  | 1GB      |

| AF2GCFI-7ACXP  | 2GB      |

| AF4GCFI-7ACXP  | 4GB      |

| AF8GCFI-7ABXP  | 8GB      |

| AF16GCFI-7ABXP | 16GB     |

| AF32GCFI-7AAXP | 32GB     |

<sup>\*</sup>Note: "P" stands for PowerProtector feature

### 1.2 Introduction

By utilizing SLC NAND flash memory and advanced Global Wear Leveling technology, the ATP Industrial Grade CompactFlash Card has enhanced endurance levels and a longer product lifespan. The ATP Industrial Grade CF card implements the StaticDataRefresh technology, which monitors the error bit levels during each read operation to ensure data integrity, and the EarlyRetirement technology prevents data loss from weak blocks.

The ATP Industrial Grade CF card has also incorporated the S.M.A.R.T. (Self-Monitoring, Analysis, and Reporting Technology) function which monitors various parameters of endurance and reliability, indicating activity that is out of the normal range. This information helps predict storage failure for preventative action.

Patent ATP PowerProtector technology is implemented in ATP industrial grade CF card to ensure a sufficient amount of backup power during power abnormalities to minimize the risk of data loss or firmware corruption.

### 1.3 Main Features

#### • Host Interface:

- λ Compliance with CF specification 4.1

- λ Pre-screened Single Level Cell (SLC) NAND flash memory

- λ True IDE mode compatible:Support PIO mode 0~6, MDMA mode 0~2, UDMA mode 0~4

#### High performance:

- λ Sequential read up to 51MByte/s (UDMA 4, Flash number x 2)

- λ Sequential write up to 25MByte/s (UDMA 4, Flash number x 2)

- λ Capacity: 512MB to 32GB

- Industrial grade temp.: -40°C to 85°C

#### • Endurance:

- λ Enhanced endurance by *Global wear leveling* and bad block management

- λ 13/24 bit BCH-ECC engines can correct up to 24 bit errors per 1,024 byte data

- $\lambda$  MTBF > 5,000,000 hours (@25°C)

- λ Data reliability: Bit error rate 10E-15 (NAND flash)

- Number of connector insertion/removals: >10,000

- StaticDataRefresh technology to assure data integrity in read operations.

- PowerProtector, built-in power-down data protection

- S.M.A.R.T. function support for life time monitor

- Power saving mode (automatic sleep and wake-up mechanism)

# 1.4 Application

ATP Industrial Grade CF cards are designed for demanding industrial applications, such as military/aerospace, automation, marine navigation, embedded systems, telecommunication equipment or networking and medical equipment where mission-critical data requires the highest level of reliability, durability, and data integrity.

# 2 Product Specification

# 2.1 System Power Requirement

Table2-1: System power table

| Voltage      | Maximum Average RMS Current    | Measurement Method |

|--------------|--------------------------------|--------------------|

| 3.3V +/- 5%  | 75mA (500mA in Power Level 1)  | 3.3V at 25°C       |

| 5.0V +/- 10% | 100mA (500mA in Power Level 1) | 5.0V at 25°C       |

# 2.2 Environment Specifications

**Table2-2: Environment Specifications**

| Туре                                |               | Standard                                     |

|-------------------------------------|---------------|----------------------------------------------|

| Tomporoturo                         | Operating     | -40°C to 85°C                                |

| Temperature                         | Non-Operating | -40°C to 85°C                                |

| Humidity                            | Storage       | 40°C, 93% RH / 500hrs<br>85°C,85%RH / 500hrs |

| Random Vibration test               | Non-Operating | 10~2000Hz, 6Grms, 30min per axis             |

| Drop test                           | Non-Operating | 150cm/Free fall                              |

| UV light exposure test (ISO 7816-1) | Non-Operating | 254nm, 15Ws/cm2                              |

# 2.3 Reliability

Table 2-3: Reliability

| Туре                      | Measurement |                                          |  |

|---------------------------|-------------|------------------------------------------|--|

| Number of insertions      | 10,000 m    | inimum                                   |  |

| Endurance                 | 100,000 I   | P/E cycles SLC NAND Flash cell endurance |  |

|                           | 512MB       | 10 terabyte random write                 |  |

|                           | 1GB         | 20 terabyte random write                 |  |

|                           | 2GB         | 40 terabyte random write                 |  |

| TBW (Total Bytes Written) | 4GB         | 80 terabyte random write                 |  |

|                           | 8GB         | 160 terabyte random write                |  |

|                           | 16GB        | 320 terabyte random write                |  |

|                           | 32GB        | 640 terabyte random write                |  |

| MTBF (@ 25°C)             | > 5,000,0   | 00 hours                                 |  |

Note: Endurance for flash cards can be predicted based on the usage conditions applied to the device, the internal NAND flash cycles, the write amplification factor, and the wear leveling efficiency of the flash devices.

### 2.4 Performance

**Table 2-4: Performance**

| Model P/N      | Seq. Read<br>(KB/s) | Seq. Write<br>(KB/s) | Random Read<br>(KB/s) | Random Write<br>(KB/s) |

|----------------|---------------------|----------------------|-----------------------|------------------------|

| AF512CFI-7ACXP | 24945               | 10742                | 24265                 | 3408                   |

| AF1GCFI-7ACXP  | 29446               | 15597                | 28464                 | 5200                   |

| AF2GCFI-7ACXP  | 30476               | 16075                | 29090                 | 5624                   |

| AF4GCFI-7ACXP  | 50319               | 19266                | 44377                 | 6285                   |

| AF8GCFI-7ABXP  | 51328               | 24945                | 44377                 | 7261                   |

| AF16GCFI-7ABXP | 51328               | 25190                | 44377                 | 7402                   |

| AF32GCFI-7AAXP | 50381               | 24945                | 43620                 | 7553                   |

Note: Tested by HDBench 3.40 beta6 with 40MB file size. The performance may vary based on different testing environments.

# 2.5 CHS Parameters

**Table 2-5 CHS Table**

|                 | SM2232AD with SLC |           |       |         |               |                   |  |

|-----------------|-------------------|-----------|-------|---------|---------------|-------------------|--|

| Product density | Flash<br>type     | Cylinders | Heads | Sectors | Total sectors | Physical capacity |  |

| 512MB           | 2K page           | 991       | 16    | 63      | 998928        | 511451136         |  |

| 1GB             | 2K page           | 1966      | 16    | 63      | 1981728       | 1014644736        |  |

| 2GB             | 2K page           | 3900      | 16    | 63      | 3931200       | 2012774400        |  |

| 4GB             | 8K page           | 7785      | 16    | 63      | 7847280       | 4017807360        |  |

| 8GB             | 8K page           | 15538     | 16    | 63      | 15662304      | 8019099648        |  |

| 16GB            | 8K page           | 31045     | 16    | 63      | 31293360      | 16022200320       |  |

| 32GB            | 8K page           | 62041     | 16    | 63      | 62537328      | 32019111936       |  |

## 2.6 Extra Features

**Table 2-6: Extra Features**

| Туре           | Measurement                                                                                                       |

|----------------|-------------------------------------------------------------------------------------------------------------------|

| ESD Proof      | Yes                                                                                                               |

| RoHS Compliant | Yes                                                                                                               |

| ESD Proof      | IEC 61000-4-2:<br>non-contact pad (Coupling plane discharge) +/- 8KV,<br>non-contact pad (Air discharge) +/- 15KV |

### 2.7 Global Wear Leveling- Longer Life Expectancy

The program / erase cycle of each sector/page/block is finite. Writing constantly on the same spot will cause the flash to wear out quickly. Furthermore, bit errors are not proportioned to P/E cycles; sudden death may occur when the block is close to its P/E cycle limit. Then unrecoverable bit errors will cause fatal data loss (especially for system data or FAT).

Global wear leveling algorithm evenly distributes the P/E cycles of each block to minimize the possibility of one block exceeding its max P/E cycles before the rest. In return, the life expectancy of memory storage device is prolonged and the chance/occurrence of unrecoverable bit errors could be reduced.

### 2.8 StaticDataRefresh Technology – Assure Data Integrity

Over time the error bits accumulate to the threshold in the flash memory cell and eventually become uncorrectable despite using the ECC engine. In the traditional handling method, the data is moved to a different location in the flash memory; despite the corrupted data is beyond repaired before the transition.

To prevent data corruption, the CF card monitors the error bit levels in each read operation; when it reaches the preset threshold value, StaticDataRefresh is achieved by erasing and re-programming the data into the same block or into another block. After the re-programming operation is completed, the controller reads the data and compares the data/parity to ensure data integrity.

### 2.9 ATP PowerProtector – Built-in Power Down Data Protection

ATP PowerProtector technology ensures a sufficient amount of reserve power during any power abnormalities such as unstable voltages and power outages. PowerProtector's patent pending technology is a stand alone hardware design that does not require specific controllers or customized firmware. This feature provides greater flexibility during the design of a smaller form factor such as CompactFlash cards.

During a sudden power failure, the drive then draws power from PowerProtector's solid state capacitors for reserve power, which guarantee reliable drive operations. The solid state capacitors allow the flash to finish processing the last command or data.

SuperCap, the traditional power protection design, is well known for its sensitivity to temperature change and has a tendency of losing its capacitance and functionality at extreme temperatures. The average life span of SuperCap is less than two years; the capacitance will degrade over time and eventually fail to perform.

ATP PowerProtector surpasses the natural limitations of SuperCap designs by supporting wide

# Your Ultimate Memory Solution!

temperature and an average life span of over five years without capacitance degradation.

PowerProtector offers an advanced level of protection ensuring that data integrity is not compromised during a power failure scenario, and preserves critical data in mission critical applications.

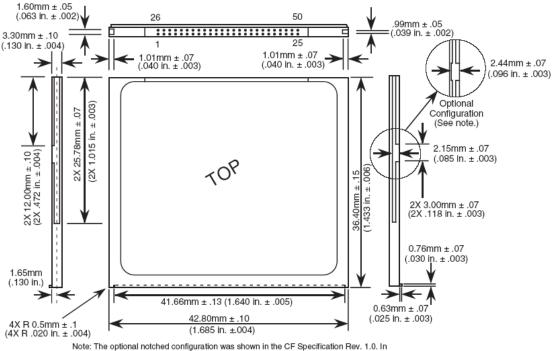

# 2.10 Physical Dimension Specification

**Table 2-7: Physical Specifications**

| Туре    |           | Measurement             |

|---------|-----------|-------------------------|

|         | Length    | $36.4$ mm $\pm 0.15$ mm |

| Tuna I  | Width     | $42.8$ mm $\pm 0.10$ mm |

| Type I  | Thickness | 3.3mm ±0.10mm           |

|         | Weight    | 9.0 g typical           |

|         | Length    | $36.4$ mm $\pm 0.15$ mm |

| Tuno II | Width     | $42.8$ mm $\pm 0.10$ mm |

| Type II | Thickness | 5.0mmMax                |

|         | Weight    | 9.0 g typical           |

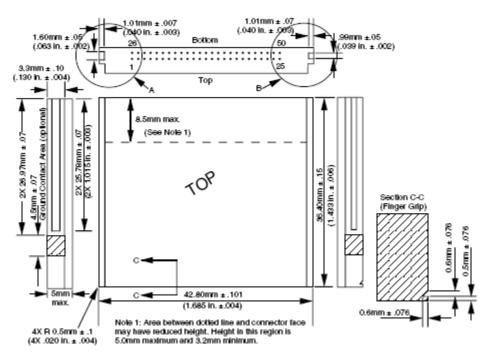

## 2.11 Mechanical Form Factor (Units in MM)

Figure 2-1: ATP CompactFlash Card Physical Dimensions

Note: The optional notched configuration was shown in the CF Specification Hev. 1.0. In specification Rev. 1.2, the notch was removed for ease of tooling. This optional configuration can be used but it is not recommended.

Type II

# 2.12 Certification and compliance

### 2.12.1 Certification table

Table 2-8: Certification table

| Mark/Approval | Documentation                                                                                                                                                                                                                                                                                                                                                                                                      | Certification |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| CE            | The CE marking (also known as CE mark) is a mandatory <u>conformance mark</u> on many products placed on the single market in the <u>European Economic Area</u> (EEA). The CE marking certifies that a product has met EU consumer safety, health or environmental requirements. CE stands for Conformité Européenne, "European conformity" in French.                                                             | Yes           |

| FC            | FCC Part 15 Class B was used for Evolution of United States (US) Emission Standards for Commercial Electronic Products, The United States (US) covers all types of unintentional radiators under Subparts A and B (Sections 15.1 through 15.199) of FCC 47 CFR Part 15, usually called just FCC Part 15                                                                                                            | Yes           |

| RoHS          | RoHS is the acronym for Restriction of Hazardous Substances. RoHS, also known as Directive 2002/95/EC, originated in the European Union and restricts the use of specific hazardous materials found in electrical and electronic products. All applicable products in the EU market after July 1, 2006 must pass RoHS compliance. For the complete directive, see Directive 2002/95/EC of the European Parliament. | Yes           |

### 3 Electrical Interface

## 3.1 Pin Assignments and Pin Type

The host is connected to the CompactFlash Card using a standard 50-pin connector. The connector in the host consists of two rows of 25 male contacts each on 50 mil (1.27 mm) centers.

The signal/pin assignments are listed in Table 3-1. Low active signals have a "-" prefix. Pin types are Input, Output or Input/Output. Section 3.3 defines the DC characteristics for all input and output type structures.

Table 3-1: Pin Assignments and Pin Type

|     | PC Card Mer    | nory Mod    | le              | PC Card I/O Mode |                  |             |                 | True IDE Mode <sup>13</sup> |                |             |                 |

|-----|----------------|-------------|-----------------|------------------|------------------|-------------|-----------------|-----------------------------|----------------|-------------|-----------------|

| Pin | Signal<br>Name | Pin<br>Type | In, Out<br>Type | Pin              | Signal<br>Name   | Pin<br>Type | In, Out<br>Type | Pin                         | Signal<br>Name | Pin<br>Type | In, Out<br>Type |

| 1   | GND            |             | Ground          | 1                | GND              |             | Ground          | 1                           | GND            |             | Ground          |

| 2   | D03            | Groun<br>d  | I1Z,OZ          | 2                | D03              | I/O         | I1Z,OZ          | 2                           | D03            | I/O         | I1Z,OZ3         |

| 3   | D04            | I/O         | I1Z,OZ          | 3                | D04              | I/O         | I1Z,OZ          | 3                           | D04            | I/O         | I1Z,OZ3         |

| 4   | D05            | I/O         | I1Z,OZ          | 4                | D05              | I/O         | I1Z,OZ          | 4                           | D05            | I/O         | I1Z,OZ3         |

| 5   | D06            | I/O         | I1Z,OZ          | 5                | D06              | I/O         | I1Z,OZ          | 5                           | D06            | I/O         | I1Z,OZ3         |

| 6   | D07            | I/O         | I1Z,OZ          | 6                | D07              | I/O         | I1Z,OZ          | 6                           | D07            | I/O         | I1Z,OZ3         |

| 7   | -CE1           | I           | I3U             | 7                | -CE1             | I           | I3U             | 7                           | -CS0           | I           | I3Z             |

| 8   | A10            | I           | I1Z             | 8                | A10              | I           | I1Z             | 8                           | $A10^{2}$      | I           | I1Z             |

| 9   | -OE            | I           | I3U             | 9                | -OE              | I           | I3U             | 9                           | -ATA SEL       | I           | I3U             |

| 10  | A09            | I           | I1Z             | 10               | A09              | I           | I1Z             | 10                          | $A09^{2}$      | I           | I1Z             |

| 11  | A08            | I           | I1Z             | 11               | A08              | I           | I1Z             | 11                          | $A08^2$        | I           | I1Z             |

| 12  | A07            | I           | I1Z             | 12               | A07              | I           | I1Z             | 12                          | $A07^{2}$      | I           | I1Z             |

| 13  | VCC            |             | Power           | 13               | VCC              |             | Power           | 13                          | VCC            |             | Power           |

| 14  | A06            | I           | I1Z             | 14               | A06              | I           | I1Z             | 14                          | $A06^2$        | I           | I1Z             |

| 15  | A05            | I           | I1Z             | 15               | A05              | I           | I1Z             | 15                          | $A05^2$        | I           | I1Z             |

| 16  | A04            | I           | I1Z             | 16               | A04              | I           | I1Z             | 16                          | $A04^2$        | I           | I1Z             |

| 17  | A03            | I           | I1Z             | 17               | A03              | I           | I1Z             | 17                          | $A03^2$        | I           | I1Z             |

| 18  | A02            | I           | I1Z             | 18               | A02              | I           | I1Z             | 18                          | A02            | I           | I1Z             |

| 19  | A01            | I           | I1Z             | 19               | A01              | I           | I1Z             | 19                          | A01            | I           | I1Z             |

| 20  | A00            | I           | I1Z             | 20               | A00              | I           | I1Z             | 20                          | A00            | I           | I1Z             |

| 21  | D00            | I/O         | I1Z,OZ          | 21               | D00              | I/O         | I1Z,OZ          | 21                          | D00            | I/O         | I1Z,OZ3         |

| 22  | D01            | I/O         | I1Z,OZ          | 22               | D01              | I/O         | I1Z,OZ          | 22                          | D01            | I/O         | I1Z,OZ3         |

| 23  | D02            | I/O         | I1Z,OZ          | 23               | D02              | I/O         | I1Z,OZ          | 23                          | D02            | I/O         | I1Z,OZ3         |

| 24  | WP             | О           | OT3             | 24               | -IOIS16          | 0           | OT3             | 24                          | -IOIS16        | О           | ON3             |

|     | PC Card Mer    | nory Mod    | le              |                  | PC Card I/O Mode |             |                 |                             | True IDE I     |             |                 |

| Pin | Signal<br>Name | Pin<br>Type | In, Out<br>Type | Pin              | Signal<br>Name   | Pin<br>Type | In, Out<br>Type | Pin                         | Signal<br>Name | Pin<br>Type | In, Out<br>Type |

| 25 | -CD2                                                    | О   | Ground | 25 | -CD2                                                    | О   | Ground | 25 | -CD2                                                               | О   | Ground                   |

|----|---------------------------------------------------------|-----|--------|----|---------------------------------------------------------|-----|--------|----|--------------------------------------------------------------------|-----|--------------------------|

| 26 | -CD1                                                    | О   | Ground | 26 | -CD1                                                    | O   | Ground | 26 | -CD1                                                               | О   |                          |

| 27 | D11 <sup>1</sup>                                        | I/O | I1Z,OZ | 27 | D11 <sup>1</sup>                                        | I/O | I1Z,OZ | 27 | D11 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 28 | D12 <sup>1</sup>                                        | I/O | I1Z,OZ | 28 | D12 <sup>1</sup>                                        | I/O | I1Z,OZ | 28 | D12 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 29 | D13 <sup>1</sup>                                        | I/O | I1Z,OZ | 29 | D13 <sup>1</sup>                                        | I/O | I1Z,OZ | 29 | D13 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 30 | D14 <sup>1</sup>                                        | I/O | I1Z,OZ | 30 | D14 <sup>1</sup>                                        | I/O | I1Z,OZ | 30 | D14 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 31 | D15 <sup>1</sup>                                        | I/O | I1Z,OZ | 31 | D15 <sup>1</sup>                                        | I/O | I1Z,OZ | 31 | D15 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 32 | -CE2 <sup>1</sup>                                       | I   | I3U    | 32 | -CE21                                                   | I   | I3U    | 32 | -CS1 <sup>1</sup>                                                  | I   | I3Z                      |

| 33 | -VS1                                                    | О   | Ground | 33 | -VS1                                                    | O   | Ground | 33 | -VS1                                                               | О   | Ground                   |

| 34 | -IORD<br>HSTROBE <sup>9</sup><br>HDMARDY <sup>10</sup>  | I   | I3U    | 34 | -IORD<br>HSTROBE <sup>9</sup><br>HDMARDY <sup>10</sup>  | I   | I3U    | 34 | -IORD <sup>6</sup><br>HSTROBE <sup>7</sup><br>HDMARDY <sup>8</sup> | I   | I3Z                      |

| 35 | -IOWR<br>STOP <sup>9,10</sup>                           | I   | I3U    | 35 | −IOWR<br>STOP <sup>9,10</sup>                           | I   | I3U    | 35 | -IOWR <sup>6</sup><br>STOP <sup>7,8</sup>                          | I   | I3Z                      |

| 36 | -WE                                                     | I   | I3U    | 36 | -WE                                                     | I   | I3U    | 36 | $-WE^3$                                                            | I   | I3U                      |

| 37 | READY                                                   | О   | OT1    | 37 | -IREQ                                                   | О   | OT1    | 37 | INTRQ                                                              | 0   | OZ1                      |

| 38 | VCC                                                     |     | Power  | 38 | VCC                                                     |     | Power  | 38 | VCC                                                                |     | Power                    |

| 39 | -CSEL <sup>4</sup>                                      | I   | I2Z    | 39 | -CSEL <sup>4</sup>                                      | I   | I2Z    | 39 | -CSEL                                                              | I   | I2U                      |

| 40 | -VS2                                                    | О   | OPEN   | 40 | -VS2                                                    | 0   | OPEN   | 40 | -VS2                                                               | О   | OPEN                     |

| 41 | RESET                                                   | I   | I2Z    | 41 | RESET                                                   | I   | I2Z    | 41 | -RESET                                                             | I   | I2Z                      |

| 42 | -WAIT<br>-DDMARDY <sup>9</sup><br>DSTROBE <sup>10</sup> | 0   | OT1    | 42 | -WAIT<br>-DDMARDY <sup>9</sup><br>DSTROBE <sup>10</sup> | 0   | OT1    | 42 | IORDY <sup>6</sup> -DDMARDY <sup>7</sup> DSTROBE <sup>8</sup>      | 0   | ON1<br>OT1 <sup>12</sup> |

| 43 | -INPACK<br>-DMARQ <sup>11</sup>                         | 0   | OT1    | 43 | -INPACK<br>-DMARQ <sup>11</sup>                         | 0   | OT1    | 43 | DMARQ                                                              | О   | OZ1                      |

| 44 | −REG<br>−DMARQ <sup>11</sup>                            | I   | I3U    | 44 | −REG<br>−DMARQ <sup>11</sup>                            | Ι   | I3U    | 44 | -DMACK <sup>5</sup>                                                | Ι   | I3U                      |

| 45 | BVD2                                                    | 0   | OT1    | 45 | -SPKR                                                   | I/O | OT1    | 45 | -DASP                                                              | I/O | I1U,ON                   |

| 46 | BVD1                                                    | О   | OT1    | 46 | -STSCHG                                                 | I/O | OT1    | 46 | -PDIAG                                                             | I/O | I1U,ON                   |

| 47 | D08 <sup>1</sup>                                        | I/O | I1Z,OZ | 47 | D08 <sup>1</sup>                                        | I/O | I1Z,OZ | 47 | D08 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 48 | D09 <sup>1</sup>                                        | I/O | I1Z,OZ | 48 | D09 <sup>1</sup>                                        | I/O | I1Z,OZ | 48 | D09 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 49 | D10 <sup>1</sup>                                        | I/O | I1Z,OZ | 49 | D10 <sup>1</sup>                                        | I/O | I1Z,OZ | 49 | D10 <sup>1</sup>                                                   | I/O | I1Z,OZ3                  |

| 50 | GND                                                     |     | Ground | 50 | GND                                                     |     | Ground | 50 | GND                                                                |     | Ground                   |

#### Notes:

- 1) These signals are required only for 16 bit accesses and not required when installed in 8 bit systems. Devices should allow for 3-state signals not to consume current.

- 2) The signal should be grounded by the host.

- 3) The signal should be tied to VCC by the host.

- 4) The -CSEL signal is ignored by the card in PC Card modes. However, because it is not pulled up on the card in these modes, it should not be left floating by the host in PC Card modes. In these modes, the pin should be connected by the host to PC Card A25 or grounded by the host.

- 5) If DMA operations are not used, the signal should be held high or tied to VCC by the host. For proper operation in older hosts: while DMA operations are not active, the card shall ignore this signal, including a floating condition

- 6) Signal usage in True IDE Mode except when Ultra DMA mode protocol is active.

- 7) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Write is active.

- 8) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Read is active.

- 9) Signal usage in PC Card I/O and Memory Mode when Ultra DMA mode protocol DMA Write is active.

- 10) Signal usage in PC Card I/O and Memory Mode when Ultra DMA mode protocol DMA Read is active.

- 11) Signal usage in PC Card I/O and Memory Mode when Ultra DMA protocol is active.

- 12) Signal is a totem-pole output during Ultra DMA data bursts in True IDE mode.

- 13) The mode is optional for CF+ Cards, but required for CompactFlash Storage Cards.

# 3.2 Electrical Description

The CompactFlash Card functions in three basic modes:

- 1) PC Card ATA using I/O Mode

- 2) PC Card ATA using Memory Mode

# Your Ultimate Memory Solution!

3) True IDE Mode, which is compatible with most disk drives.

ATP Industrial CompactFlash Card supports all three modes. The configuration of the CompactFlash Card is controlled using the standard PCMCIA configuration registers starting at address 200h in the Attribute Memory space of the storage card or for True IDE Mode, pin 9 being grounded.

**Table 3-2: Signal Description**

| SIGNAL NAME                                     | DIR. | PIN                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------|------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 - A0<br>(PC Card Memory Mode)               | I    | 8,10,11,12,<br>14,15,16,17,<br>18,19,20 | These address lines along with the -REG signal are used to select the following: The I/O port address registers within the CompactFlash Card, the memory mapped port address registers within the CompactFlash Card, a byte in the card's information structure and its configuration control and status registers. |

| A10 - A0<br>(PC Card I/O Mode)                  |      |                                         | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                          |

| A2 - A0<br>(True IDE Mode)                      |      | 18,19,20                                | In True IDE Mode, only A[2:0] are used to select the one of eight registers in the Task File, the remaining address lines should be grounded by the host.                                                                                                                                                           |

| BVD1<br>(PC Card Memory Mode)                   | I/O  | 46                                      | This signal is asserted high, as BVD1 is not supported.                                                                                                                                                                                                                                                             |

| -STSCHG<br>(PC Card I/O Mode)<br>Status Changed |      |                                         | This signal is asserted low to alert the host to changes in the READY and Write Protect states, while the I/O interface is configured. Its use is controlled by the Card Config and Status Register.                                                                                                                |

| -PDIAG<br>(True IDE Mode)                       |      |                                         | In the True IDE Mode, this input / output is the Pass Diagnostic signal in the Master / Slave handshake protocol.                                                                                                                                                                                                   |

| BVD2<br>(PC Card Memory Mode)                   | I/O  | 45                                      | This signal is asserted high, as BVD2 is not supported.                                                                                                                                                                                                                                                             |

| -SPKR<br>(PC Card I/O Mode)                     |      |                                         | This line is the Binary Audio output from the card. If the Card does not support the Binary Audio function, this line should be held negated.                                                                                                                                                                       |

| -CD1, -CD2<br>(PC Card Memory Mode)             | 0    | 26,25                                   | These Card Detect pins are connected to ground on the CompactFlash Card. They are used by the host to determine that the CompactFlash Card is fully inserted into its socket.                                                                                                                                       |

| SIGNAL NAME | DIR. | PIN | DESCRIPTION |

|-------------|------|-----|-------------|

|-------------|------|-----|-------------|

| whether a byte or a word operation is being performed. CFL2 always accesses the che odd byte of the word. CFL accesses the even byte to Odd byte of the word depending on A0 and -CF2. A multiplexing scheme based on A0, -CF1, -CF2 allows 8 bit hosts to access all data on D0-D7.  This signal is the same as the PC Card Memory Mode signal.  -CSQ, -CSI (True IDE Mode)  -CSQ, -CSI (True IDE Mode)  -CSI: (True IDE Mode)  -CSI: (PC Card Memory Mode)  -CSEL (PC Card Memory Mode)  -CSEL (PC Card I/O Mode)  -CSEL (PC Card I/O Mode)  -CSEL (PC Card I/O Mode)  -CSEL (PC Card Memory Mode)  -CSEL -C | -CE1, -CE2         | I   | 7,32                           | These input signals are used both to select the card and to indicate to the card                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CSI , -CE2 (PC Card I/O Mode) Card Enable  -CSO, -CS1 (True IDE Mode)  -CSO, -CS1 (True IDE Mode)  -CSI is used to select the Alternate Status Register and the Device Control Register. While -DMACK is asserted, -CSO and -CSI shall be held negated and the width of the transfers shall be 16 bits.  -CSEL (PC Card Memory Mode)  -CSEL (PC Card Memory Mode)  -CSEL (PC Card I/O Mode)  -CSEL (This signal is not used for this mode, but should be connected by the host to PC Card A25 or grounded by the host.  -CSEL (PC Card I/O Mode)  -CSEL (This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Slave.  -CSEL (PC Card Memory Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |     |                                | whether a byte or a word operation is being performedCE2 always accesses the odd byte of the wordCE1 accesses the even byte or the Odd byte of the word depending on A0 and -CE2. A multiplexing scheme based on A0, -CE1, |

| -CSI , -CE2 (PC Card I/O Mode) Card Enable  -CSO, -CS1 (True IDE Mode)  -CSO, -CS1 (True IDE Mode)  -CSI is used to select the Alternate Status Register and the Device Control Register. While -DMACK is asserted, -CSO and -CSI shall be held negated and the width of the transfers shall be 16 bits.  -CSEL (PC Card Memory Mode)  -CSEL (PC Card Memory Mode)  -CSEL (PC Card I/O Mode)  -CSEL (This signal is not used for this mode, but should be connected by the host to PC Card A25 or grounded by the host.  -CSEL (PC Card I/O Mode)  -CSEL (This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Slave.  -CSEL (PC Card Memory Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |     |                                | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                 |

| CSL   is used to select the Alternate Status Register and the Device Control Register. While -DMACK is asserted, -CSO and -CS1 shall be held negated and the width of the transfers shall be 16 bits.    CSEL   (PC Card Memory Mode)   This signal is not used for this mode, but should be connected by the host to PC Card L/O Mode)   This signal is not used for this mode, but should be connected by the host to PC Card L/O Mode)   This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device is configured as a Master. When the pin is open, this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device as a Master or a Slave when configured in the True IDE Mode. When this device is configured as a Master. When the pin is open, the same as the PC Card M   | (PC Card I/O Mode) |     |                                |                                                                                                                                                                                                                            |

| PC Card Memory Mode)  -CSEL (PC Card I/O Mode)  -CSEL (This signal is not used for this mode, but should be connected by the host to PC Card I/O Mode)  -CSEL (True IDE Mode)  This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave.  D15 - D00 (PC Card Memory Mode)  D15 - D00 (PC Card I/O Mode)  D15 - D00 (PC Card I/O Mode)  This signal is the same as the PC Card Memory Mode signal.  In True IDE Mode, all Task File operations occur in byte mode on the low order bus D[7:0] while all data transfers are 16 bit using D[15:0].  GND (PC Card I/O Mode)  GND (PC Card I/O Mode)  This signal is the same for all modes.  This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |     |                                | -CS1 is used to select the Alternate Status Register and the Device Control Register.  While –DMACK is asserted, -CS0 and –CS1 shall be held negated and the                                                               |

| PC Card I/O Mode)  -CSEL (True IDE Mode)  I/O 31,30,29,28, (PC Card Memory Mode)  I/O This signal is the same as the PC Card Memory Mode signal.  In True IDE Mode, all Task File operations occur in byte mode on the low order bus D[7:0] while all data transfers are 16 bit using D[15:0].  GND (PC Card I/O Mode)  GND (PC Card I/O Mode)  This signal is the same for all modes.  This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    | I   | 39                             |                                                                                                                                                                                                                            |

| A Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave.  D15 - D00 (PC Card Memory Mode)  D15 - D00 (PC Card I/O Mode)  D15 - D00 (True IDE Mode, all Task File operations occur in byte mode on the low order bus D[7:0] while all data transfers are 16 bit using D[15:0].  GND (PC Card I/O Mode)  This signal is the same for all modes.  This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |     |                                |                                                                                                                                                                                                                            |

| PC Card Memory Mode   27,49,48,47, 6,5,4,3,2,23, 22,21   host and the controller. D00 is the LSB of the Even Byte of the Word. D08 is the LSB of the Odd Byte of the Word.    D15 - D00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |     |                                | a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is                                                                       |

| (PC Card I/O Mode)  D15 - D00 (True IDE Mode)  In True IDE Mode, all Task File operations occur in byte mode on the low order bus D[7:0] while all data transfers are 16 bit using D[15:0].  GND (PC Card Memory Mode)  This signal is the same for all modes.  GND (PC Card I/O Mode)  This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    | I/O | 27,49,48,47,<br>6,5,4,3,2, 23, | host and the controller. D00 is the LSB of the Even Byte of the Word. D08 is                                                                                                                                               |

| GND (PC Card Memory Mode)  GND (PC Card I/O Mode)  GND (PC Card I/O Mode)  This signal is the same for all modes.  This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |     |                                | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                 |

| (PC Card Memory Mode)  GND (PC Card I/O Mode)  This signal is the same for all modes.  GND  This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |     |                                | In True IDE Mode, all Task File operations occur in byte mode on the low order bus D[7:0] while all data transfers are 16 bit using D[15:0].                                                                               |

| (PC Card I/O Mode)  GND  This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |     | 1,50                           | Ground.                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |     |                                | This signal is the same for all modes.                                                                                                                                                                                     |

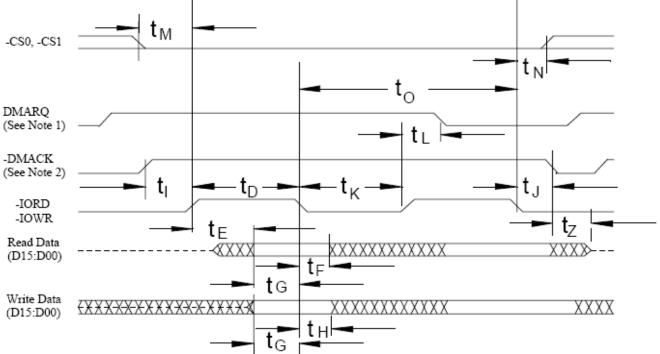

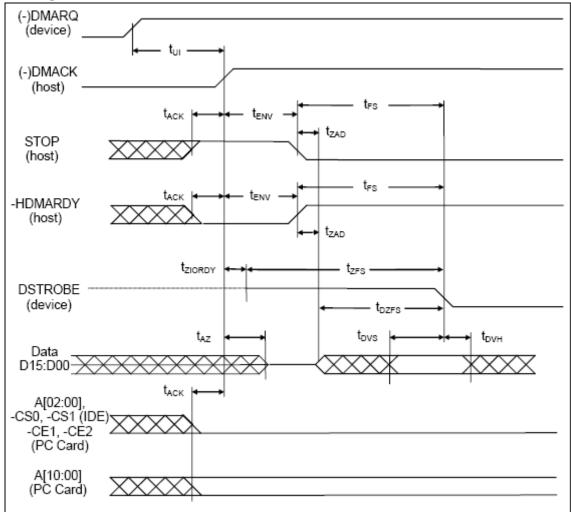

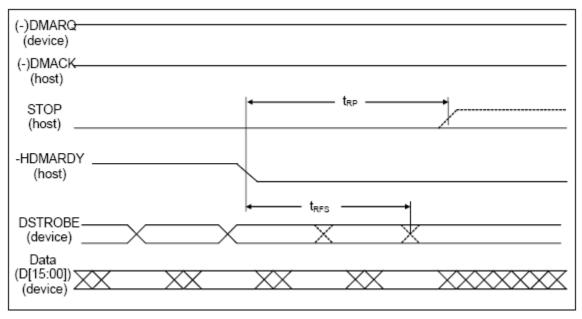

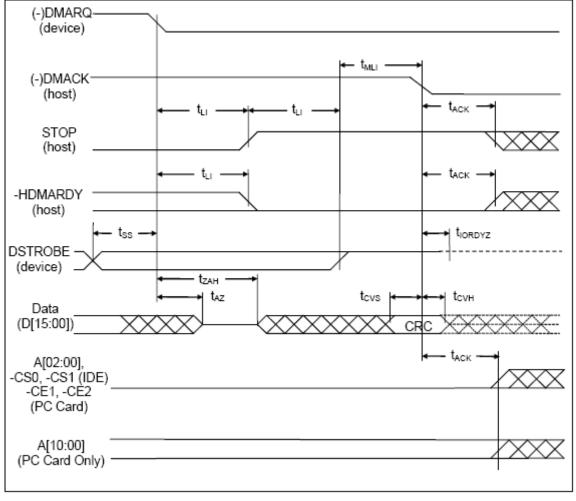

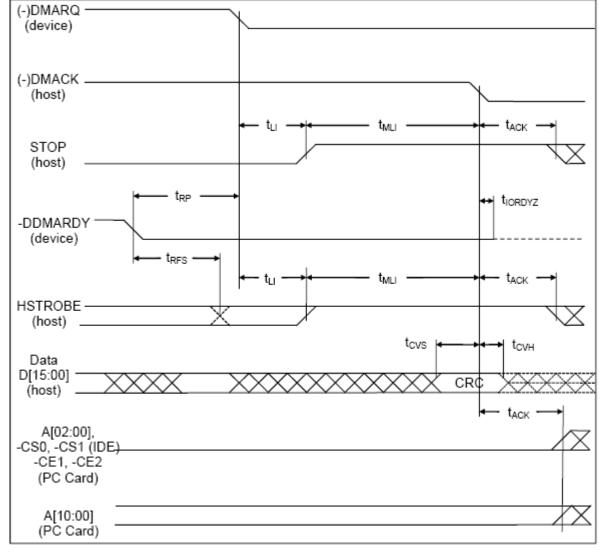

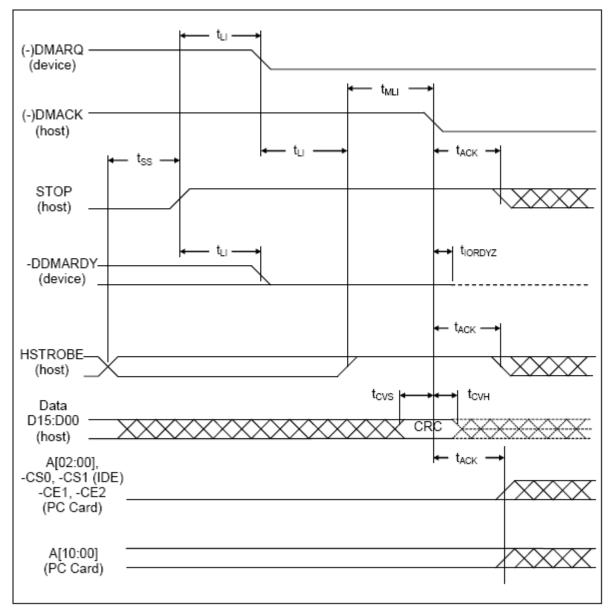

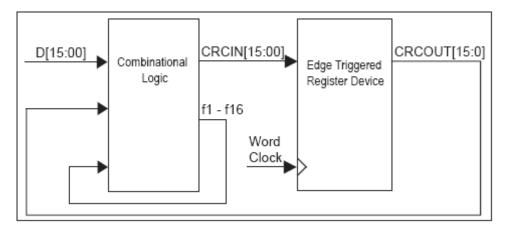

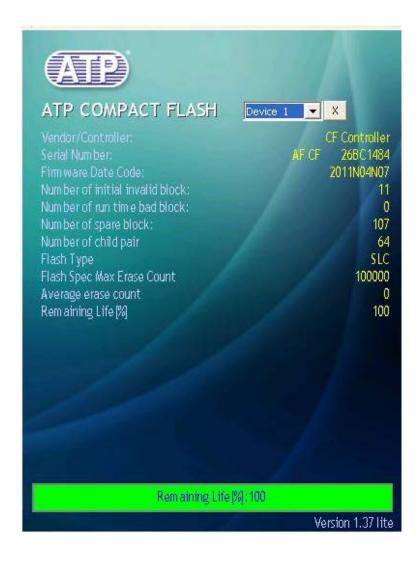

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |     |                                | This signal is the same for all modes.                                                                                                                                                                                     |